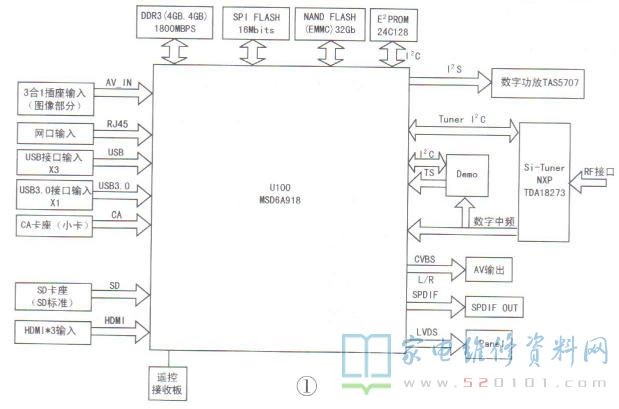

创维8S90机芯的主板采用MSD6A918(U100),该芯片内置四核ARM cortex-A9 CPU(最高1.5GHz)、六核ARM Mali- 450 GPU及2GDDR3,具有3D蓝光解码技术,支持3D转2D;支持2T USB、32G SD;支持All- HD单芯片一体机,DIMB地面数字电视;内置千兆双频WIFI、蓝牙4.0、WIFI Direct;支持天赐派、微信点播、多屏云享MHL;具有DTS数字影院系统,支持手势、语音、空鼠交互等功能,其组成如图1所示。

一、开机流程分析

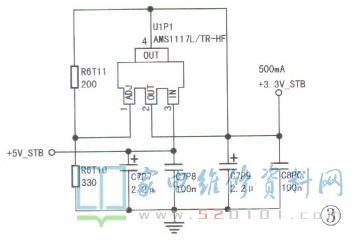

该机芯主板的供电系统如图2所示,其开机流程如下:

(1)电源板送+5V_ STB供电给主板。

(2)+5V_ STB经过UIPO变换后得到+3.3V_STB电压,供给CPU;另外,+3.3V_ STB还给背光控制、SPIFLASH等电路供电。

(3)CPU(U100)的供电脚得到供电,复位脚得到复位电压后,外围晶振起振,CPU开始工作,SPI FLASH(UOM3)开始工作,U100内的主控系统与UOM3进行通讯,然后主控制器运行UOM3内的启动程序( Mboot)。

(4)U100工作后,CPU的部分IO引脚会输出默认电平,其中,C2脚输出PWR-ON/OFF开机信号(高电平),经Q0S3.Q0S4倒相后送往电源反。

(5)电源板得到PWR-ON/OFF开机信号后,电源电路开始工作,输出+24V、+20V、12V_ Normal供电。

(6)+12V_ NOR经U1328变换后输出+1.2V,供给u100;12V_ Normal经U1316、 UOP6变换后输出+5V,再经过U1P2、UOP8、U1005变换得到+3.3V和+1.5V_ DDR电压。

(7)主控系统对NANDFLASH、EPROM、DDR3SDRAM进行初始化。

(8)主控系统与DDR通讯,将NAND FLASH中的主程序装载到DDR中,并运行主程序。

(9)主控系统开始对各类寄存器进行初始化,检测音响等总线连接,并对其初始化。

(10)主控系统从UOM2中读取用户程序数据。

(11 )初始化完成后,系统处于开机状态。

二、单元电路分析

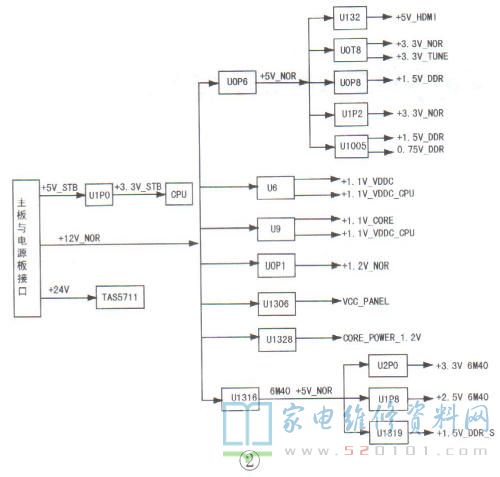

1. +3.3V_ Standby供电电路

电源板副电源电路送来的+5V_STB供电经UIP1(AMS117L/TR-HF )稳压,得到+3.3V_ STB供电,供给U100( MSD6A918)中的待机CPU,如图3所示。

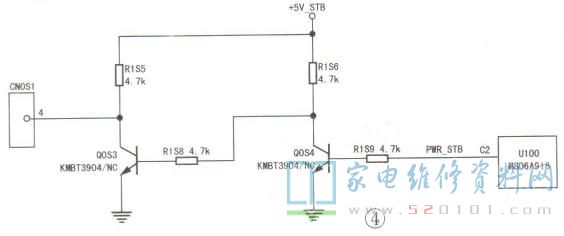

2.开/关机控制电路

U100工作后,其C2脚输出M_ PWR. ON/OFF开机信号(高电平),于是Q0S4的集电极输出低电平、Q0S3的集电极输出高电平(sTAND_ BY开机信号),该信号经插座CN0S1④脚送往电源板,如图4所示。

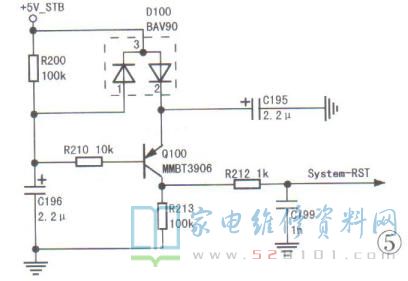

3.复位电路

+5V_ STB 供电分两路送给复位电路,如图5所示:一路经D100给C195充电,待充满电后给Q100的发射极供电;另一路经R209给C196充电,待充满后经R210给Q100的基极供电,于是Q100由截止变为饱和导通。随着C196不断充电,Q100会由饱和导通变为截止,即U100的复位脚( B1 )的电平由低电平变为高电平,然后又变为低电平,从而完成高电平复位。

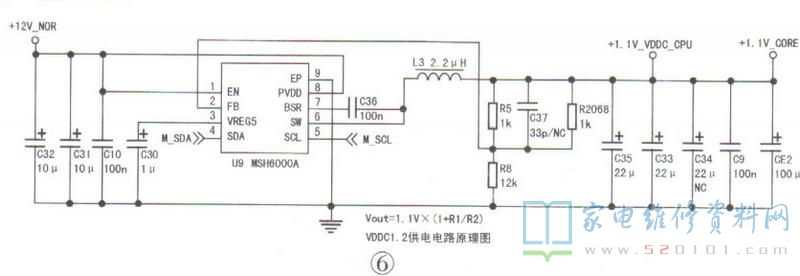

4. VDDC供电产生电路

电源板输出的+12V. NOR供电经过以U9为核心的DC-DC电路变换,得到+1.1V_VD-DC_ .CPU和+1.1V_ cORE电压,供给CPU内核电路,如图6所示。

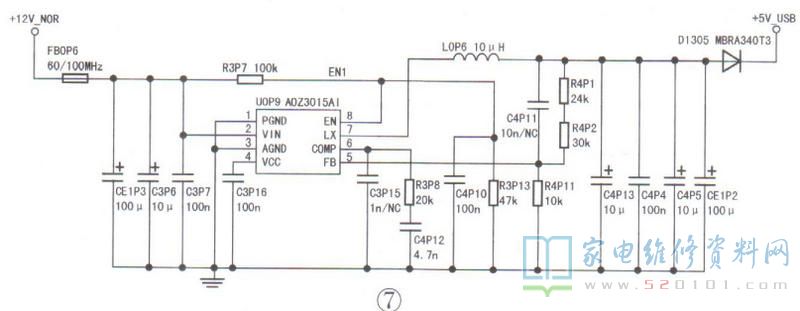

5. USB供电电路

电源板输出的+12V_ NOR供电经过以UOP9为核心的DC DC电路变换,得到+5V_ USB供电,供给主板上的USB电路,如图7所示。

6. EPROM电路

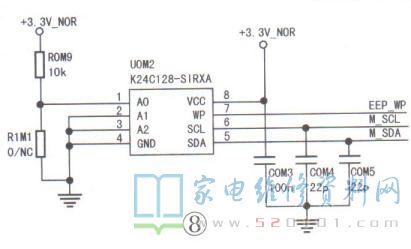

该机芯EPROM电路如图8所示,UOM2用于存储用户设置、开机状态、MAC地址、KEY码、数字电视序列号、串货条码等信息,其⑤脚为串行数据线脚,⑥脚为串行时钟线脚,⑦脚为写保护控制脚。

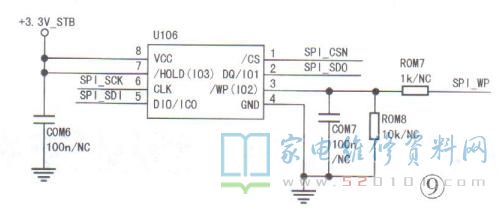

7.SPI FLASH电路

该机芯的SPI FLASH电路如图9所示,U106 是一款16Mbit串行FLASH,用于存储开机引导程序,其①脚为片选控制输入脚,②脚为串行数据输入/输出脚,③脚为写保护控制脚,④脚为接地脚,⑤脚为串行数据输入/输出脚,⑥脚为时钟输入脚,⑦脚为暂停控制脚,⑧脚为供电脚。

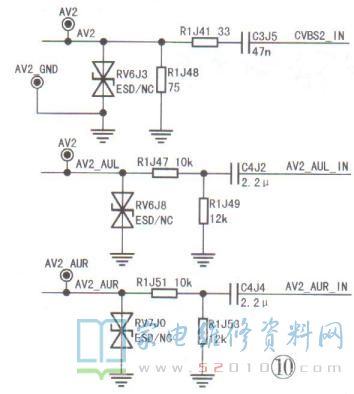

8.AV信号输入电路

视频信号由JA1J9的④脚输入,经RV6J3防静电、R1J48阻抗匹配R1J41隔离,C3J5耦合后,送到主芯片U100的AC6脚,如图10所示。

右音频信号从JA1J9③脚输入,经RV7J0防静电、R1J51隔离、R1J53阻抗匹配、C4J4耦合后,送到U100的AK1脚。左音频信号由JA1J9②脚输入,经RV6J8防静电R1J47隔离、R1J49阻抗匹配,C4J2耦合后,送到U100的AK2脚。

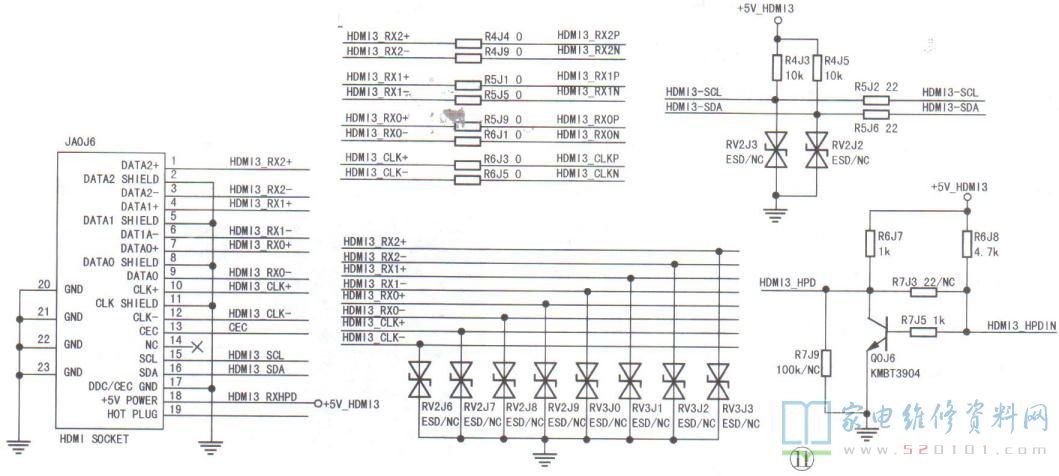

9. HDMI信号输入电路

如图11所示,HDMI3_ RX2+信号从插座JAO]6①脚输入,经R4]4隔离后送到U100的W3脚,HDMI3_ RX2-信号由JA0J6③脚输入,经R4T9隔离后送到U100的W2脚;HDMI3_ RX1+信号由JA0J6④脚输入,经RSJ1隔离后送到U100的W1脚,HDMI3. RX1-信号由JA0J6⑥脚输入,经R5J5隔离后送到U100的V3脚;HDMI3_ RX0+信号由JAOJ6⑦脚输入,经R5J9隔离后送到U100的V1脚,HDMI3_RX0-信号由JA0J6⑨脚输入,经R6J1隔离后送到U100的V2脚;HDMI3_CLK+信号由JA0J6①脚输入,经R6J3隔离后送到U100的U3脚;HD-MI3_CLK-信号由JA0J6 12脚输入,经R6J5隔离后送到U100的U2脚。

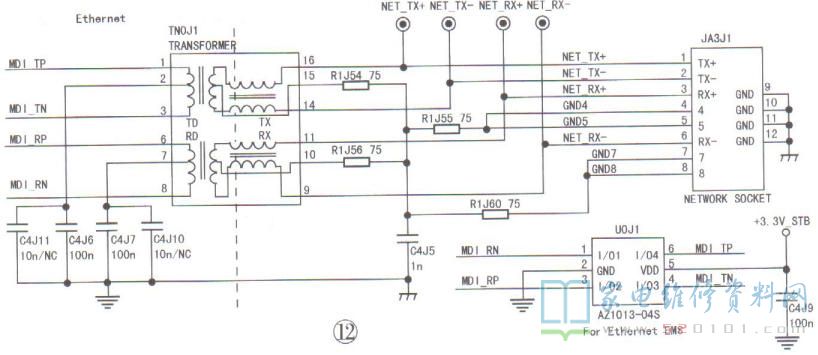

10. NET(网络)信号输入电路

网络信号从插座JA3J1输入,经TNOJ1变压后送往U100,如图12所示。

TX+、TX-、 RX+、RX-信号分别由JA9①、②、③、⑥脚输入,送到TNOJ1 16、14、11、9脚,经U10]1隔离变压后从①、③、⑥、⑧脚分别输出MDI_TP、MDI_TN、MDL_ RP、MDL_RN信号,送到U100的J1J2、H3、H2脚。

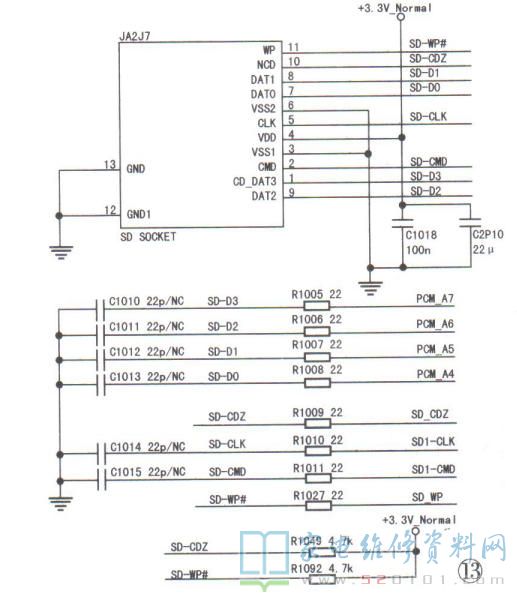

11. SD卡信号输入电路

SD卡信号从插座JA2]7输入,送往主芯片U100,如图13所示。

SD-D0 信号从JA2J]7⑦脚输入,经R1008隔离后送到U100的AH12脚;SD-D1信号从JA2J7⑧脚输入,经R1007隔离后送到U100的AJ11脚;SD-D2信号从JA2J7⑨脚输入,经R1006隔离后送到U100的AH11脚;SD-D3 信号从JA2]7①脚输入,经R1005隔离后送到u100的AG12脚;SD- cDZ信号从JA2J7的10脚输入,经R1009隔离后送到U100的P5脚;SD-CLK信号从JA2j7⑤脚输入,经R1010隔离后送到U100的AG21脚;SD-CMD信号从JA2j7②脚输入,经R1011隔离后送到U100的AG20脚;SD-WP#信号从JA2J7①脚输入,经R1027隔离后送到U100的B4脚。

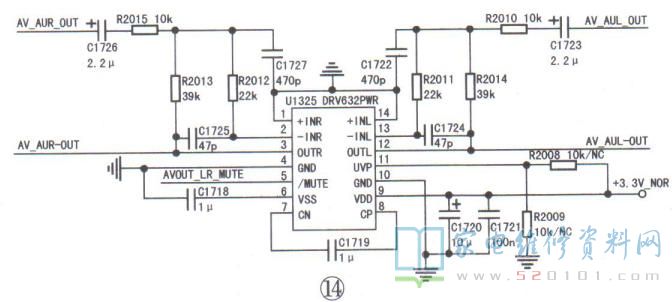

12.AV信号输出电路

U100的AM4脚送来的右音频信号经C1726耦合,R2015隔离后送给U1325进行比较放大, 然后输出;U100的AL4脚送来的左音频信号,经C1723耦合.R2010隔离R2011隔离U1325放大,然后输出。相关电路如图14所示。

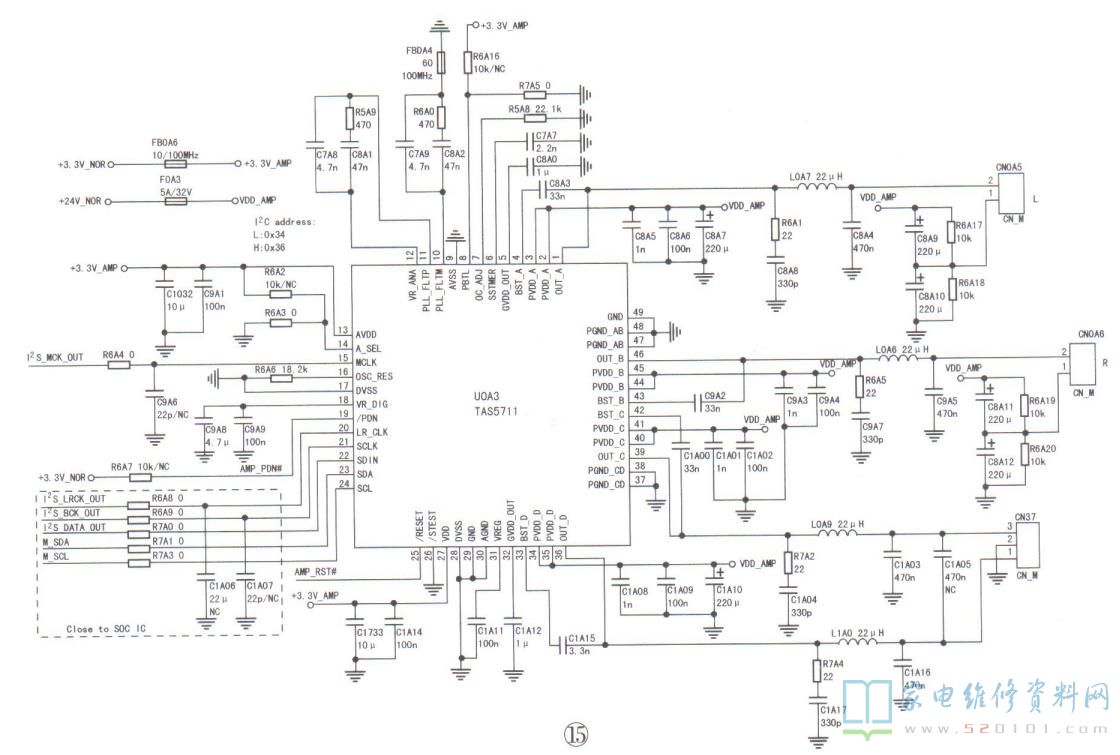

13.数字音频功放电路

本机芯伴音功放采用数字音频功放TAS511,如图15所示。

UOA3(TAS5711)内部集成了数字音频处理、串行音频端口、数字音频接口、串行控制、微控制、SRC、降噪、功放输出、保护逻辑等电路,其2、3、34、35、40、41、44、45的脚为24V供电脚,17脚为3.3V模拟供电脚,8、27脚为3.3V数字供电脚,19(PND )脚是待机控制脚,25(RESET )脚是复位脚, 23(SDA)脚,24(SCL )脚为数据、时钟总线脚,15(MCLK)脚为主时钟输入脚,20(LR_CLK)脚为串行音频数据左右时钟输入脚,21(SCLK )脚为串行音频数据时钟输入脚,22(SDIN)脚为串行音频数据输入脚,1(OUT_A)脚、46(OUT_B )脚分别为左、右声道音频信号输出脚,36(OUT D)、39(OUT C)脚分别为左、右重低音音频信号输出脚,其中,15、20、21、22脚是IIS数字音频信号输入脚。

Q0A1及其外围元件组成复位电路。在需要复位时,U100的AL15脚输出M_ AMP-RST复位控制信号,经Q0A1、R2A0、C386控制,给写脚一个复位电压。Q0A2、Q0A4及其外围元件组成静音控制电路。关机后,+24V电压快速消失,Q0A4基极电压下降较快,当Q0A4基极电压下降到饱和导通电压时,Q0A4饱和导通,C1737上的电压经Q0A4的发射极到集电极,再经R2A7,送给Q0A2基极一个高电平,于是Q0A2饱和导通,其集电极由高电平变为低电平,即U0A3 25脚变为低电平,从而实现关机静音。