1. 简介

KB2511B是Samsung公司生产的用于数字偏转处理(DDP)的芯片,外形为32脚双列直插封装,是I2C总线控制的单片集成行场处理IC,它控制了所有与行场偏转处理有关的功能电路,其外围电路极其简单,特别适合于15寸和17寸高端显示器的行场处理,其部分功能如下所示。

该芯片内部含有行、场频锁相环振荡器,其行自由振荡频率决定于KB2511B(5)CO脚行振荡器外接电容和(6)RO脚行振荡器外接电阻,场自由振荡频率决定于(22)VCAP脚场锯齿波发生器外接形成电容,自由振荡器根据IC(1)(2)脚输入的行场同步信号,对其输出的行、场驱动信号进行锁相同步,行频率最大可达150KHZ, 场部分可进行50-165HZ AGC回路控制。

该芯片具备了很强的几何较正功能,在I2C总线数据的控制下,可对图像几何形状进行调整,包括场幅、场线性、场中心、场S校正、东西枕校、梯形校正、弓形校正、平行四边形校正、动态聚焦调整等等。

该芯片还有X-射线保护功能,当 IC(25)XRAY脚的电压高于8V时,X-射线保护起作用,行输出停止,此种保护方式对主电源不起作用,不用此功能时需将该脚接地。

IC(18)BREATH脚可对束流取样,可根据束流变化对场幅度进行校正,保证了图像亮暗变化时场幅的稳定。

IC(24)EWOUT脚输出的枕校波形为交流的,不包含行幅信息,所以S#、MT#外加一运放TA75559来叠加CPU板B26脚HSIZE输出的行幅信息,并进行预放大。

IC在断开总线SDA、SCL与HSYNC/VSYNC行场同步的情况下,可独立工作,此项功能可用以作故障判断。

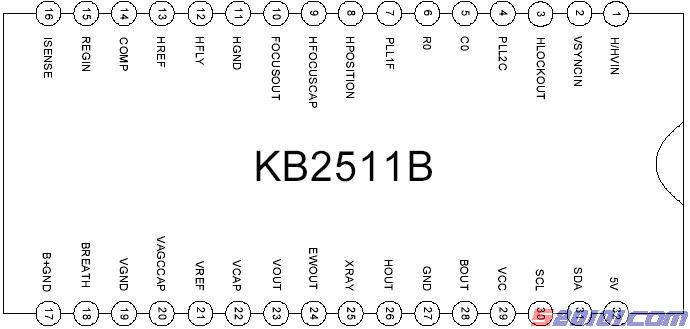

3.引脚功能

引脚 |

符号 |

功能 |

| 1 |

H/HVIN |

TTL compatible horizontal sync input(Separate or composite)行同步输入端 |

| 2 |

VSYNCIN |

TTL compatible vertical sync input (for separated H&V)场同步输入端 |

| 3 |

HLOCKOUT |

First PLL lock/unlock output (0V unlocked - 5V locked)一级锁相环状态确认输出端(0V:没锁定-5V:锁定) |

| 4 |

PLL2C |

Second PLL loop filter二级锁相环回路滤波端 |

| 5 |

CO |

Horizontal oscillator capacitor行振荡器外接电容端 |

| 6 |

RO |

Horizontal oscillator resistor行振荡器外接电阻端 |

| 7 |

PLL1L |

First PLL loop filter一级锁相环回路滤波端 |

| 8 |

HPOSITION |

Horizontal position filter(Capacitor to be connected to HGND)行中心滤波端(外接电容到行模块地) |

| 9 |

HFOCUSCAP |

Horizontal dynamic focus oscillator capacitor行动态聚焦振荡器外接电容端 |

| 10 |

FOCUSOUT |

Mixed horizontal and vertical dynamic focus output行场动态聚焦叠加输出端 |

| 11 |

HGND |

Horizontal Section Ground内部行模块地 |

| 12 |

HFLY |

Horizontal Flyback Input (positive polarity)行反馈输入端 |

| 13 |

HREF |

Horizontal Section Reference Voltage (to be filtered)内部行模块基准电压滤波端 |

| 14 |

COMP |

B+ error amplifier output for frequency compensation and gain setting B+误差放大器输出(用于频率补偿和增益设置) |

| 15 |

REGIN |

Regulation input of B+ control loop B+控制回路的调节输入端 |

| 16 |

ISENSE |

Sensing of external B+ switching transistor current or switch for step-down converter B+电流感应端 |

| 17 |

B+GND |

Ground (related to B+ reference adjustment)地(与B+基准调节有关) |

| 18 |

BREATH |

DC breathing input control(Compensation of vertical amplitude against EHV variation)瞬间直流输入控制端(高压变化对场幅的补偿) |

| 19 |

VGND |

Vertical section ground内部场模块地 |

| 20 |

VAGCCAP |

Memory capacitor for automatic gain control loop in vertical ramp generator场锯齿波发生器自动增益回路的外接存储电容端 |

| 21 |

VREF |

Vertical section reference voltage (to be filtered)场模块的基准电压滤波端 |

| 22 |

VCAP |

Vertical sawtooth generator capacitor场锯齿波发生器外接形成电容端 |

| 23 |

VOUT |

Vertical ramp output (with frequency independent amplitude and S or C corrections if any). It is mixed with vertical position voltage and vertical moire.场锯齿波输出端(有与频率无关的幅度和S/C校正),含场中心和莫尔效应校正。 |

| 24 |

EWOUT |

Pincushion-East/West correction parabola output东西枕校抛物波输出端 |

| 25 |

XRAY |

X-RAY protection input (with internal latch function)X射线保护输入 |

| 26 |

HOUT |

Horizontal drive output (internal transistor, open collector)行驱动输出端 |

| 27 |

GND |

General ground (referenced to Vcc)供电地 |

| 28 |

BOUT |

B+ PWM regulator output B+脉宽调整输出端 |

| 29 |

VCC |

Supply voltage (12V typ)供电端(一般12V) |

| 30 |

SCL |

I2C clock input I2C时钟线输入端 |

| 31 |

SDA |

I2C data input I2C数据线输入端 |

| 32 |

5V |

Supply voltage (5V typ)供电端(一般5V) |

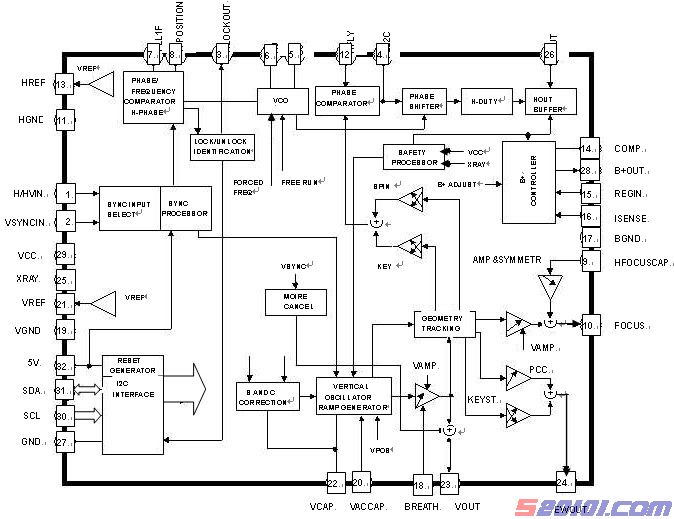

4.内部框图 [Page]

英文注释:

VREF -》基准电压, PHASE/ FREQUENCY COMPARATOR/ H-PHASE -》相位/频率比较器/行-相位,

VCO -》压控振荡器, PHASE COMPARATOR -》相位比较器, PHASE SHIFTER -》移相器,

H -DUTY -》行占空因数, HOUT BUFFER -》行输出缓冲器,

L OCK/UNLOCK IDENTIFICATION -》锁定/没锁定 确认, FORCED FREQ -》受控频率,

FREE RUN -》自由振荡, SAFETY PROCESSOR -》安全处理器, B+ CONTROLLER -》B+控制器,

B+ ADJUST -》B+调整, SYNC INPUT SELECT -》同步输入选择, SYNC PROCESSOR -》同步处理器, SPIN -》旋转, KEY -》梯形, AMP&SYMMETR -》放大与对称, GEOMETRY TRACKING -》几何跟踪 , VAMP -》场放大, KEY -》梯形失真, PCC -》枕形失真校正电路,

MOIRE CANCEL -》莫尔条纹取消, RESET GENERATOR -》复位发生器, I2C INTERFACE-》I2C接口,

VERTICAL OSCILLATOR /RAMP GENERATOR -》场振荡器/锯齿波发生器,

S AND C CORRECTION -》场S校正和场中心校正